Master clock frequencies and jitter performance

Quote from Pedja on 19 March 2019, 9:35 PMTrying to help on choosing the master clock frequencies, and hence the maximum sampling rate supported by Audial USB DACs, an S4 DAC page has been recently updated with graphs that show the bit clock performance separately for 11.2896 and 22.5792 MHz master clocks.

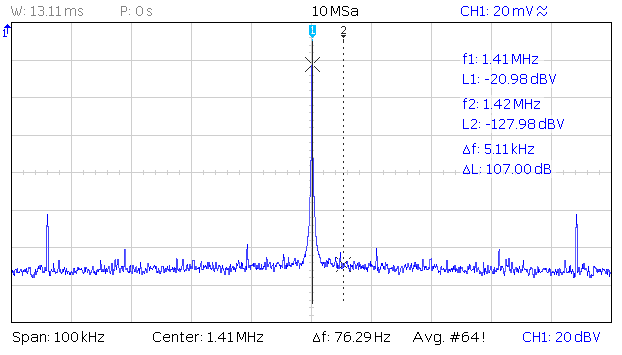

11.2896 MHz:

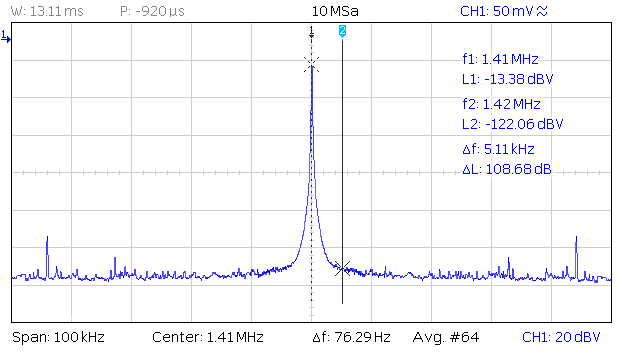

22.5792 MHz:

So, the skirt looks more narrow with 11.2896 MHz. Eldam could be right on spot here:

https://www.audialonline.com/blog/another-story-about-tda1541a-384-khz/comment-page-1/#comment-4536Â

I hope this will indeed help rather than confuse. To sum it up, the best sound I heard was from 352.8 / 384 kHz recordings. On the other hand, I remain to prefer the lowest possible master clock frequencies. Mind you, an 11.2896 / 12.288 MHz master clocks still yield up to 192 kHz compatibility.

Trying to help on choosing the master clock frequencies, and hence the maximum sampling rate supported by Audial USB DACs, an S4 DAC page has been recently updated with graphs that show the bit clock performance separately for 11.2896 and 22.5792 MHz master clocks.

11.2896 MHz:

22.5792 MHz:

So, the skirt looks more narrow with 11.2896 MHz. Eldam could be right on spot here:

https://www.audialonline.com/blog/another-story-about-tda1541a-384-khz/comment-page-1/#comment-4536Â

I hope this will indeed help rather than confuse. To sum it up, the best sound I heard was from 352.8 / 384 kHz recordings. On the other hand, I remain to prefer the lowest possible master clock frequencies. Mind you, an 11.2896 / 12.288 MHz master clocks still yield up to 192 kHz compatibility.

Quote from Guest on 25 March 2019, 6:43 PMInteresting measurments Pedja. Could you tell what measure instrument do you use, so if these are the results from a specialized standalone spectrum analyzer or can be done on some other device?

I assume these are the measurments taken of the BCK with 44.1 sampling. Interesting would be to see how changes the spectrum just on the clock output and after passing the multiplexer vs the master clock frequency. Do you know why deltaF on both measurments is written the same?

Interesting measurments Pedja. Could you tell what measure instrument do you use, so if these are the results from a specialized standalone spectrum analyzer or can be done on some other device?

I assume these are the measurments taken of the BCK with 44.1 sampling. Interesting would be to see how changes the spectrum just on the clock output and after passing the multiplexer vs the master clock frequency. Do you know why deltaF on both measurments is written the same?

Quote from Bartek on 25 March 2019, 6:59 PMAs I see editing posts doesnt seem to work.. have to write another post -

Last question came to my mind - dont we want to measure Latch rather than BCK?

As I see editing posts doesnt seem to work.. have to write another post -

Last question came to my mind - dont we want to measure Latch rather than BCK?

Quote from Guest on 26 March 2019, 3:35 PMThe DEM reclocking has an important part also in the hearing result. I don't like it after having tried on the AYAII 2014. But the further layouts since the DS edition are better on that point. In the case of AYA 2014 I had to use a uf-l wire (so screened) between the resistor and the active part of the DEM circuit to try to stay close to the behavior of a pcb trace. I believe one should try with and without the DEM reclocking circuit in order to know what they like best. I don't know if that experience is good for the AYA above the 2014 edition as I only have the 2014 pcb.

It is because the latch could be more important that the Bck only for the PCM dac chips ? I don't know, I'm just happy with no DEM reclocking as I have a clean simultaenous feeding signal for the TDA1541A. For me the DEM given too much boomy bass and less tight. Surely others devices around the AYA also are dictating their behavior in my subjectiv testimonial.

Regards, Eldam

The DEM reclocking has an important part also in the hearing result. I don't like it after having tried on the AYAII 2014. But the further layouts since the DS edition are better on that point. In the case of AYA 2014 I had to use a uf-l wire (so screened) between the resistor and the active part of the DEM circuit to try to stay close to the behavior of a pcb trace. I believe one should try with and without the DEM reclocking circuit in order to know what they like best. I don't know if that experience is good for the AYA above the 2014 edition as I only have the 2014 pcb.

It is because the latch could be more important that the Bck only for the PCM dac chips ? I don't know, I'm just happy with no DEM reclocking as I have a clean simultaenous feeding signal for the TDA1541A. For me the DEM given too much boomy bass and less tight. Surely others devices around the AYA also are dictating their behavior in my subjectiv testimonial.

Regards, Eldam

Quote from Pedja on 26 March 2019, 5:12 PM@bartek

It is Rohde & Schwarz scope. Once R&S merged with Hameg they took over the scope production too, and their HMO series (now replaced with RTB2000) introduced great low noise A/D front end and respectable FFT, thus making a great spectrum analyzer as well. Not on par with the latest dedicated phase noise analyzers, but a very versatile tool for sure.

Yes, the fS was 44.1 kHz. Delta f is a resolution in the frequency domain.

I showed a bit clock since earlier published graphs were a bit clock, so I believe this is easier to compare. A word clock / latch spectrum analysis is not more indicative here anyhow.

As for post editing, it is possible during the first 30 minutes only.

It is Rohde & Schwarz scope. Once R&S merged with Hameg they took over the scope production too, and their HMO series (now replaced with RTB2000) introduced great low noise A/D front end and respectable FFT, thus making a great spectrum analyzer as well. Not on par with the latest dedicated phase noise analyzers, but a very versatile tool for sure.

Yes, the fS was 44.1 kHz. Delta f is a resolution in the frequency domain.

I showed a bit clock since earlier published graphs were a bit clock, so I believe this is easier to compare. A word clock / latch spectrum analysis is not more indicative here anyhow.

As for post editing, it is possible during the first 30 minutes only.

Quote from Bartek on 26 March 2019, 6:41 PMI see, in this context measuring the latch is less meaningful. But probably we can also deduce that the higher the clock noise the higher the jitter of the latch?

I guess the spectrum of the BCK in some way also influence the analogue output. As I learned already its _not_ that the digital inputs have nothing to the analog output and it is not only the jitter thing, in such complicated mixed signal devices as DACs..

@Eldam: The latch on TDA in simultaneous mode is the same important and have the same role as in the PCM/AD - the moment of latching the sample on the analogue output. The BCK is used only for shifting in the samples to the registers, and if you use the internal DEM, also ( but indirectly) for the clocking of the DEM. For your try my recommendation is to switch to dem reclocking with 4x Dem ratio. Maybe you will like it better (like me). The typical cap dem is resulting in dem freq about 174-200khz (4x). And in the standard application on the aya, with dem reclocking, with the usb input you have 88khz (2x).

Greets

I see, in this context measuring the latch is less meaningful. But probably we can also deduce that the higher the clock noise the higher the jitter of the latch?

I guess the spectrum of the BCK in some way also influence the analogue output. As I learned already its _not_ that the digital inputs have nothing to the analog output and it is not only the jitter thing, in such complicated mixed signal devices as DACs..

@Eldam: The latch on TDA in simultaneous mode is the same important and have the same role as in the PCM/AD - the moment of latching the sample on the analogue output. The BCK is used only for shifting in the samples to the registers, and if you use the internal DEM, also ( but indirectly) for the clocking of the DEM. For your try my recommendation is to switch to dem reclocking with 4x Dem ratio. Maybe you will like it better (like me). The typical cap dem is resulting in dem freq about 174-200khz (4x). And in the standard application on the aya, with dem reclocking, with the usb input you have 88khz (2x).

Greets

Quote from Pedja on 27 March 2019, 1:08 AMI guess you are referring to that the output of TDA1541A working in simultaneous data mode is triggered by the LE, and not by the BCK. In the AYA 4 and in the S4 the LE and BCK performance is however tightly related, since they both are reclocked by the same flip-flop, which is clocked by the same master clock.

However, if I published LE performance, it would take some math to scale the performance of 44.1 kHz LE of USB stage, and 2.8224 MHz clock of S/PDIF stage.

And sure, by the principles of the same very math, the TD1541A output performance is directly related to the performance of the clock it uses for conversion.

And yes, in my experience it worth to reclock all the lines going to TDA, not only the clock that triggers its output. I am not sure if we have a convincing explanation for this yet.

I guess you are referring to that the output of TDA1541A working in simultaneous data mode is triggered by the LE, and not by the BCK. In the AYA 4 and in the S4 the LE and BCK performance is however tightly related, since they both are reclocked by the same flip-flop, which is clocked by the same master clock.

However, if I published LE performance, it would take some math to scale the performance of 44.1 kHz LE of USB stage, and 2.8224 MHz clock of S/PDIF stage.

And sure, by the principles of the same very math, the TD1541A output performance is directly related to the performance of the clock it uses for conversion.

And yes, in my experience it worth to reclock all the lines going to TDA, not only the clock that triggers its output. I am not sure if we have a convincing explanation for this yet.

Quote from Bartek on 28 March 2019, 12:45 PMHi Pedia, Yes that was my point. Yeah, I know the architecture of the whole isolator/reclocker and I like it very much - I had to investigate it in details to be able to test things like stopped clock and applying on board both slower and faster clock to switch beside the selection from the xmos.

Like the rest of the aya the isolator/reclocker module is a great place for diy experimemts. Now my worry is if passing the clocks via multiplexer (vhc, but in general not a clock dedicated fanout) doesnt introduce more noise/jitter, especially for higher frequency clock. Might be thats why powering the digital modules from battery makes so big difference (in the same time just being cleaner power source for the clock).

In the following days/weeks I'm going to test the external programmable clock (so at the end without the need of muxes), also in few weeks I will hopefully have in my hands a 16GS scope with dedicated jitter analysis (said to about 5ps - maybe still not enough :)), so I will definitely share my results of my experiments (If there will be any 🙂 ).

Hi Pedia, Yes that was my point. Yeah, I know the architecture of the whole isolator/reclocker and I like it very much - I had to investigate it in details to be able to test things like stopped clock and applying on board both slower and faster clock to switch beside the selection from the xmos.

Like the rest of the aya the isolator/reclocker module is a great place for diy experimemts. Now my worry is if passing the clocks via multiplexer (vhc, but in general not a clock dedicated fanout) doesnt introduce more noise/jitter, especially for higher frequency clock. Might be thats why powering the digital modules from battery makes so big difference (in the same time just being cleaner power source for the clock).

In the following days/weeks I'm going to test the external programmable clock (so at the end without the need of muxes), also in few weeks I will hopefully have in my hands a 16GS scope with dedicated jitter analysis (said to about 5ps - maybe still not enough :)), so I will definitely share my results of my experiments (If there will be any 🙂 ).

Quote from Bartek on 28 March 2019, 2:43 PMand Pedja, one question to you, here a good place for it - have you tried the simultaneous mode with the LE going up for the last halfperiod of the last clock in 16 bit frame? - like it is shown in the TDA1541A datasheet? Not especially on 352, but on any samplerate in general. Then it would need 2x slower clock for any samplerate. Didn't you like it, or it didn't worked or just found 32bit frame easier to implement?

and Pedja, one question to you, here a good place for it - have you tried the simultaneous mode with the LE going up for the last halfperiod of the last clock in 16 bit frame? - like it is shown in the TDA1541A datasheet? Not especially on 352, but on any samplerate in general. Then it would need 2x slower clock for any samplerate. Didn't you like it, or it didn't worked or just found 32bit frame easier to implement?