TDA1541A DEM clocking

Quote from Pedja on 3 December 2021, 12:44 PMIt has been more than half a year since we started shipping the S5 DAC, and as I promised some of you, here is the public reply regarding some news brought by the S5 design.

The first is about the TDA1541A DEM circuit clocking: as you know, the S5 abandoned synchronous DEM clocking. Also, the latest AYA 5 DAC project includes the required circuit on the board but does not actually include it in the typical configuration, leaving it as an optional feature instead. So, why did it turn out like that?

First, about the DEM (Dynamic Element Matching) itself. It denotes the circuit which interchanges the currents in time, to produce the equal resulting currents. Several articles written by Philips engineers back in the '70s and '80s describe such an approach.

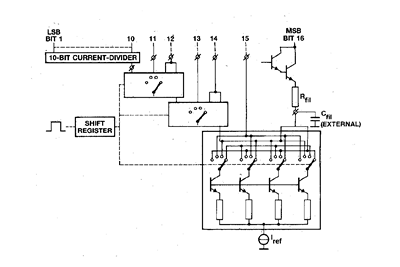

Figure 2 you will find in the Schouwenaars, Dijkmans, Kup, and van Tuijl's "A Monolithic Dual 16-Bit D/A Converter" can not be more informative on this. Please note the bottom right part of the drawing, marked by the rectangle. This way, four possibly unequal current source outputs, interchanged in time, produce four equal currents.

Of course, such a circuit requires some oscillator to work. For this purpose, the TDA1541A includes a bistable multivibrator, whose frequency is controlled by the external capacitor. (Original TDA1541, non-A, employed this capacitor inside.) The frequency generally recommended by Philips is between 150 kHz and 300 kHz, with the bottom limit at 80 kHz (it is internally divided by four, as also implied by the above picture, and this divided-by-four frequency should not come inside the audio band), while above 300 kHz the performance slightly deteriorates (very slightly though, and mostly at the bottom end).

Typically, a capacitor of 470 pF is used to set this frequency to about 200 kHz. And this is the typical setup too, that makes a "free-running" oscillator, meaning that it is not in any way associated with the digital audio stream clocking.

The same capacitor nodes can, however, also be used to connect the external source for this oscillator frequency. And I was using the external circuits to clock the TDA1541A synchronously with the audio stream, for more than 10 years, in the Model S, S USB, S Mk2 and S Mk3, S4, and AYA 4, as well as in several other AYA projects as an optional feature. Now, why this "step back"?

The first reason, chronologically speaking, was practical, and associated with the move from CS8414 to CS8416 S/PDIF receiver. Some will say "a somewhat late move", but to my defense, I actually used CS8416 years ago, in D-09, where I needed up to 192 kHz capable S/PDIF receiver. With TDA1541A, this really was no requirement, and since CS8416 brought no major performance improvements (besides its ability to lock on preamble), I just stuck with CS8414, so long as it was possible. Now, since the CS8414 became somewhat tricky to source, and I also wanted more inputs, I found CS8416 again useful.

Now, what did this change about the synchronous DEM clocking? The CS8416, with its PLL unlocked, outputs lower (bit and word) clock frequencies than the CS8414. Since my synchronous DEM clock is tied to the bit clock, and the DEM clock is, as said above, also further divided internally by four by the TDA1541A, its final frequency falls notably inside the audio band, and DEM becomes "audible". Practically speaking, when you select BNC or optical input and do not connect anything there, you will experience a sort of noise. Although it is relatively low in level, and it stops once the audio stream starts, such things give the impression of a "poor design".

CS8416 also offers a way out of this, but it requires one more oscillator, and I was reluctant about that, as there are already several HF sources inside, and I paid a lot of attention to put them all under control.

So, many years later, and taking into account the S5 as an environment, I switched this back (and then forth, and then back), to revise the sonic effects of synchronous DEM clocking.

And, synchronous and classic DEM clocking definitely draw somewhat different sonic pictures. Synchronous clocking brings more sharp edges and positioning. The bass gets not only more tightened, but it also feels better tuned, in a way it never sounds like one-note. I especially liked this in a time when opinions on the muddy or woolly bass performance of TDA1541A practically prevailed. (I knew that such fame rather came from many other parts of TDA1541A circuit designs I've seen - all the way from the early Philips CDs through the "advanced" output stage designs with tubes - but, you know...)

My later designs, according to the customers' feedback, also brought more resolution, in a way that really does not leave anything to be missed. Removing synchronous and applying again free-running clocking for DEM, at this time showed some good sides of it: a bigger scale, more ambiance, and more velvet tone. Cymbals are interesting, as they are probably not that sparkling like with synchronous clocking, but are actually cleaner, and also have more body at that. It is, maybe not entirely, but a sort of Paiste vs Zildjian case. And although they tonally act a bit differently, both these options, in the current circumstances, have the same or similar overall definition.

Finally, my decision for S5 was to proceed with a free-running clock for DEM. The AYA 5 also uses free-running DEM by default, but since it is partially intended for DIY endeavors and systems, where things can be individually tweaked, it also keeps synchronous clocking as an optional feature.

It has been more than half a year since we started shipping the S5 DAC, and as I promised some of you, here is the public reply regarding some news brought by the S5 design.

The first is about the TDA1541A DEM circuit clocking: as you know, the S5 abandoned synchronous DEM clocking. Also, the latest AYA 5 DAC project includes the required circuit on the board but does not actually include it in the typical configuration, leaving it as an optional feature instead. So, why did it turn out like that?

First, about the DEM (Dynamic Element Matching) itself. It denotes the circuit which interchanges the currents in time, to produce the equal resulting currents. Several articles written by Philips engineers back in the '70s and '80s describe such an approach.

Figure 2 you will find in the Schouwenaars, Dijkmans, Kup, and van Tuijl's "A Monolithic Dual 16-Bit D/A Converter" can not be more informative on this. Please note the bottom right part of the drawing, marked by the rectangle. This way, four possibly unequal current source outputs, interchanged in time, produce four equal currents.

Of course, such a circuit requires some oscillator to work. For this purpose, the TDA1541A includes a bistable multivibrator, whose frequency is controlled by the external capacitor. (Original TDA1541, non-A, employed this capacitor inside.) The frequency generally recommended by Philips is between 150 kHz and 300 kHz, with the bottom limit at 80 kHz (it is internally divided by four, as also implied by the above picture, and this divided-by-four frequency should not come inside the audio band), while above 300 kHz the performance slightly deteriorates (very slightly though, and mostly at the bottom end).

Typically, a capacitor of 470 pF is used to set this frequency to about 200 kHz. And this is the typical setup too, that makes a "free-running" oscillator, meaning that it is not in any way associated with the digital audio stream clocking.

The same capacitor nodes can, however, also be used to connect the external source for this oscillator frequency. And I was using the external circuits to clock the TDA1541A synchronously with the audio stream, for more than 10 years, in the Model S, S USB, S Mk2 and S Mk3, S4, and AYA 4, as well as in several other AYA projects as an optional feature. Now, why this "step back"?

The first reason, chronologically speaking, was practical, and associated with the move from CS8414 to CS8416 S/PDIF receiver. Some will say "a somewhat late move", but to my defense, I actually used CS8416 years ago, in D-09, where I needed up to 192 kHz capable S/PDIF receiver. With TDA1541A, this really was no requirement, and since CS8416 brought no major performance improvements (besides its ability to lock on preamble), I just stuck with CS8414, so long as it was possible. Now, since the CS8414 became somewhat tricky to source, and I also wanted more inputs, I found CS8416 again useful.

Now, what did this change about the synchronous DEM clocking? The CS8416, with its PLL unlocked, outputs lower (bit and word) clock frequencies than the CS8414. Since my synchronous DEM clock is tied to the bit clock, and the DEM clock is, as said above, also further divided internally by four by the TDA1541A, its final frequency falls notably inside the audio band, and DEM becomes "audible". Practically speaking, when you select BNC or optical input and do not connect anything there, you will experience a sort of noise. Although it is relatively low in level, and it stops once the audio stream starts, such things give the impression of a "poor design".

CS8416 also offers a way out of this, but it requires one more oscillator, and I was reluctant about that, as there are already several HF sources inside, and I paid a lot of attention to put them all under control.

So, many years later, and taking into account the S5 as an environment, I switched this back (and then forth, and then back), to revise the sonic effects of synchronous DEM clocking.

And, synchronous and classic DEM clocking definitely draw somewhat different sonic pictures. Synchronous clocking brings more sharp edges and positioning. The bass gets not only more tightened, but it also feels better tuned, in a way it never sounds like one-note. I especially liked this in a time when opinions on the muddy or woolly bass performance of TDA1541A practically prevailed. (I knew that such fame rather came from many other parts of TDA1541A circuit designs I've seen - all the way from the early Philips CDs through the "advanced" output stage designs with tubes - but, you know...)

My later designs, according to the customers' feedback, also brought more resolution, in a way that really does not leave anything to be missed. Removing synchronous and applying again free-running clocking for DEM, at this time showed some good sides of it: a bigger scale, more ambiance, and more velvet tone. Cymbals are interesting, as they are probably not that sparkling like with synchronous clocking, but are actually cleaner, and also have more body at that. It is, maybe not entirely, but a sort of Paiste vs Zildjian case. And although they tonally act a bit differently, both these options, in the current circumstances, have the same or similar overall definition.

Finally, my decision for S5 was to proceed with a free-running clock for DEM. The AYA 5 also uses free-running DEM by default, but since it is partially intended for DIY endeavors and systems, where things can be individually tweaked, it also keeps synchronous clocking as an optional feature.

Quote from Berny on 9 December 2021, 9:25 PMHello Pedja, thank you for this sharing. For this "free-running" oscillator, are you always using the typical 470 pF? I suppose you have experience with different values, willing to share? Running synchronus currently, I get sometimes some slight modulated noise (only when watching movies with the spdif input, reconnecting solves the issue) and by reading this I'm tempted to try the free-running again :-).

I remember also you could stabilise a bit the freerunning ossilator by pulling down the pins, but the capacitance needed to be modified a bit. I need to look it up again, too long ago.

Hello Pedja, thank you for this sharing. For this "free-running" oscillator, are you always using the typical 470 pF? I suppose you have experience with different values, willing to share? Running synchronus currently, I get sometimes some slight modulated noise (only when watching movies with the spdif input, reconnecting solves the issue) and by reading this I'm tempted to try the free-running again :-).

I remember also you could stabilise a bit the freerunning ossilator by pulling down the pins, but the capacitance needed to be modified a bit. I need to look it up again, too long ago.

Quote from Pedja on 10 December 2021, 12:02 PMHello Berny,

With the AYA II 2014 (you have this one, if I am not mistaken), where this feature is optional, and several outputs from the binary counter are available, so long as you choose the proper output, you should not have any noise. Having said this, the noise may also mean that the DEM oscillator does not work at all (?).

My synchronous DEM clocking is hooked to the bit clock (in all the DACs using it, excepting the Model S USB, where it was connected to the master clock), so a DEM frequency normally changes with the sampling frequency: but I just did not find the DEM frequency crucial, so long as it is kept within specified limits.

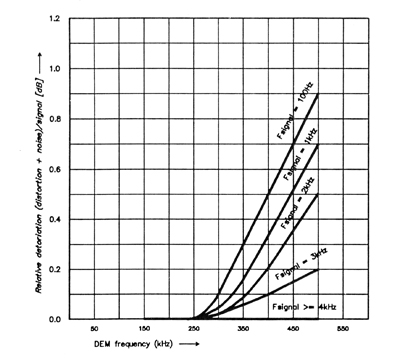

For the free-running option, yes, I am using a typical 470 pF. I am not sure if free-running / async DEM clocking frequency can change the results any significantly, but to me it just did not look very important. BTW, according to Philips' paper, the performance slightly deteriorates above 250 kHz because of the "lower duty cycle accuracy" (today we normally call this jitter) of the DEM oscillator, so the currents are not interchanged equally. Anyhow, the result showing the impact of the DEM frequency increases as the audio frequency decreases is interesting.

My general impression of sync vs free-running DEM is that the cleaner the environment (digital signal, supplies, output stage, etc.), the better the chances for a free-running DEM.

Regards

Hello Berny,

With the AYA II 2014 (you have this one, if I am not mistaken), where this feature is optional, and several outputs from the binary counter are available, so long as you choose the proper output, you should not have any noise. Having said this, the noise may also mean that the DEM oscillator does not work at all (?).

My synchronous DEM clocking is hooked to the bit clock (in all the DACs using it, excepting the Model S USB, where it was connected to the master clock), so a DEM frequency normally changes with the sampling frequency: but I just did not find the DEM frequency crucial, so long as it is kept within specified limits.

For the free-running option, yes, I am using a typical 470 pF. I am not sure if free-running / async DEM clocking frequency can change the results any significantly, but to me it just did not look very important. BTW, according to Philips' paper, the performance slightly deteriorates above 250 kHz because of the "lower duty cycle accuracy" (today we normally call this jitter) of the DEM oscillator, so the currents are not interchanged equally. Anyhow, the result showing the impact of the DEM frequency increases as the audio frequency decreases is interesting.

My general impression of sync vs free-running DEM is that the cleaner the environment (digital signal, supplies, output stage, etc.), the better the chances for a free-running DEM.

Regards

Quote from smaudio on 21 September 2024, 9:08 AMHello pedja

I built miro dac with TDA1541 NON-A , digital circuit on this dac stop clock with shifts register and i use xmos base usb i2s module for simultaneous mode.

All decoupling cap is 470nF, when I the play music high frequency is noisy after check all parts not seen the problem,so i put the 680pF MKT cap on TDA1541 osc pin and sound became clean .May i have your opinion about this problem?

Hello pedja

I built miro dac with TDA1541 NON-A , digital circuit on this dac stop clock with shifts register and i use xmos base usb i2s module for simultaneous mode.

All decoupling cap is 470nF, when I the play music high frequency is noisy after check all parts not seen the problem,so i put the 680pF MKT cap on TDA1541 osc pin and sound became clean .

May i have your opinion about this problem?

Quote from Pedja on 21 September 2024, 3:09 PMThe non-A version of TDA1541 supposedly includes the capacitor that drives the DEM oscillator, and it does not require anything connected to pins 16 & 17, as these pins have no internal connections.

If your non-A TDA1541 chip produces noise with pins 16 & 17 left open, it may be among those series never documented in Philips papers. I did hear about the non-A pieces not having that cap inside.

As we discussed in the other topic, you can hear (and measure) non-operational DEM as a noise/distortion in the presence of the audio signal. If noise appears without an audio signal, it is rather something else. Please see the post #33.

https://www.audialonline.com/community/topic/aya-2-list-mods/?part=4#postid-284

The non-A version of TDA1541 supposedly includes the capacitor that drives the DEM oscillator, and it does not require anything connected to pins 16 & 17, as these pins have no internal connections.

If your non-A TDA1541 chip produces noise with pins 16 & 17 left open, it may be among those series never documented in Philips papers. I did hear about the non-A pieces not having that cap inside.

As we discussed in the other topic, you can hear (and measure) non-operational DEM as a noise/distortion in the presence of the audio signal. If noise appears without an audio signal, it is rather something else. Please see the post #33.

https://www.audialonline.com/community/topic/aya-2-list-mods/?part=4#postid-284